一文弄懂半导体掩膜版制造工艺及流程

半导体掩膜版是集成电路制造中不可或缺的关键部件,它承担着将电路设计图案转移到硅片上的重要任务。掩膜版的制造过程涉及计算机软硬件及外围设备制造技术的紧密融合,本文将从工艺原理、主要流程和技术要点三个方面进行详细解析,帮助读者全面理解这一精密工艺。

一、掩膜版制造的基本原理与重要性

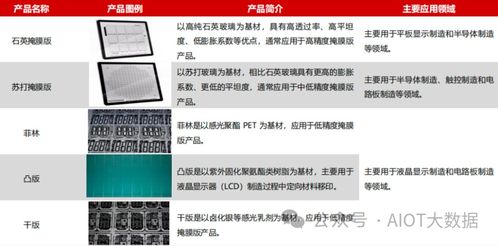

掩膜版是光刻工艺的核心工具,其制造精度直接影响芯片的性能和良率。它本质上是一块高纯度石英或玻璃基板,上面覆盖着一层遮光材料(如铬层),通过精密图案化处理形成电路设计图形。在光刻过程中,光线透过掩膜版的透明区域,将图案投射到涂有光刻胶的硅片上,实现电路的微缩复制。

掩膜版制造依赖于先进的计算机辅助设计(CAD)软件和精密硬件设备。设计阶段使用EDA工具生成电路布局,再通过图形数据处理系统转换为掩膜版可识别的格式。硬件方面,需要高精度激光直写设备、电子束曝光系统等外围设备来确保图案的精确转移。

二、掩膜版制造的主要工艺流程

掩膜版制造是一个多步骤的精密过程,主要包括以下关键环节:

1. 基板准备与清洗

选择高平坦度、低缺陷的石英或玻璃基板,经过严格的清洗和表面处理,去除微粒和污染物,确保基板表面洁净度达到纳米级别。

2. 遮光层沉积

通过物理气相沉积或化学气相沉积技术,在基板上均匀涂覆一层遮光材料(如铬),厚度通常为50-100纳米。这一层将用于形成电路图案的遮光部分。

3. 光刻胶涂覆

在遮光层上旋涂一层光敏性光刻胶,厚度需精确控制,以保证后续曝光和显影的精度。

4. 图案曝光

使用电子束直写或激光直写设备,根据CAD数据将电路图案曝光到光刻胶上。这一步骤对精度要求极高,需在无尘、恒温恒湿的超净环境中进行。

5. 显影与刻蚀

曝光后的光刻胶经过显影液处理,去除已曝光或未曝光部分(取决于光刻胶类型),形成图案模板。随后通过干法或湿法刻蚀技术,将图案转移到下方的遮光层。

6. 光刻胶去除与清洗

使用化学溶剂或等离子体去除剩余的光刻胶,并对掩膜版进行彻底清洗,确保表面无残留物。

7. 缺陷检测与修复

利用自动光学检测系统扫描掩膜版表面,识别图案缺陷。对于微小缺陷,可使用聚焦离子束或激光修复技术进行修正。

8. 保护膜涂覆与最终检验

在完成图案化的掩膜版表面涂覆一层透明保护膜(pellicle),防止灰尘污染。最后进行全面的尺寸、套刻精度和缺陷密度检验,确保产品符合规格要求。

三、计算机软硬件在掩膜版制造中的关键作用

掩膜版制造高度依赖计算机软硬件及外围设备的支持:

- 软件方面:EDA工具用于电路设计;图形数据处理软件将设计数据转换为曝光设备可识别的格式;制造执行系统管理整个生产流程。

- 硬件方面:高精度电子束或激光直写机实现纳米级图案转移;自动检测设备确保质量可控;环境控制系统维持稳定的温湿度条件。

四、技术挑战与发展趋势

随着芯片制程不断微缩,掩膜版制造面临诸多挑战:图案尺寸缩小至纳米级,对曝光精度和缺陷控制要求更高;复杂的三维结构设计需要多层掩膜版精准对准。极紫外光刻掩膜版、计算光刻技术和人工智能辅助缺陷检测将成为行业发展的重要方向。

半导体掩膜版制造是一个集成了材料科学、精密工程和计算机技术的复杂过程。只有深入理解其工艺原理和流程,并充分利用先进的软硬件工具,才能生产出满足现代芯片制造需求的优质掩膜版,推动半导体产业持续进步。

如若转载,请注明出处:http://www.jingxin-keji.com/product/10.html

更新时间:2026-03-03 08:25:09